# 1.8 Volt Intel® Wireless Flash Memory with 3 Volt I/O and SRAM (W30)

28F6408W30, 28F3204W30, 28F320W30, 28F640W30

# **Preliminary Datasheet**

# **Product Features**

#### ■ Flash Performance

- 70 ns Initial Access Speed

- 25 ns Page-Mode Read Speed

20 ns Burst-Mode Read Speed

- Burst and Page Mode in All Blocks and across All Partition Boundaries

- **Enhanced Factory Programming:** 3.5 µs per Word Program Time

- Programmable WAIT Signal Polarity

#### Flash Power

- $V_{CC}$  = 1.70 V 1.90 V  $V_{CCQ}$  = 2.20 V 3.30 V Standby Current = 6  $\mu$ A (typ.)

- Read Čurrent = 7 mÅ (4 word burst, typ.)

#### Flash Software

- 5/9 µs (typ.) Program/Erase Suspend Latency

- Time Intel® Flash Data Integrator (FDI) and Common Flash Interface (CFI) Compatible

#### Quality and Reliability

- Operating Temperature:

- -25 °C to +85 °C

- 100K Minimum Erase Cycles

- 0.18 µm ETOX<sup>TM</sup> VII Process

#### Flash Architecture

- Multiple 4-Mbit Partitions

- Dual Operation: RWW or RWE Parameter Block Size = 4-Kword

- Main block size = 32-Kword

- Top and Bottom Parameter Devices

#### ■ Flash Security

- 128-bit Protection Register: 64 Unique Device Identifier Bits; 64 User OTP Protection Register Bits

- Absolute Write Protection with V<sub>PP</sub> at Ground

- Program and Erase Lockout during Power

- Individual and Instantaneous Block Locking/ Unlocking with Lock-Down

#### SRAM

- 70 ns Access Speed

- 16-bit Data Bus

- Low Voltage Data Retention

- $-S-V_{CC} = 2.20 \text{ V} 3.30 \text{ V}$

- Density and Packaging

32-Mbit Discrete in VF BGA Package

- 64-Mbit Discrete in µBGA\* Package

- 56 Active Ball Matrix, 0.75 mm Ball-Pitch in μBGA\* and VF BGA Packages

- 32/4-, 64/8- and 128/TBD- Mbit (Flash + SRAM) in a 80-Ball Stacked-CSP Package (14 mm x 8 mm)

- 16-bit Data Bus

The 1.8 Volt Intel®Wireless Flash Memory with 3 Volt I/O combines state-of-the-art Intel® Flash technology with low power SRAM to provide the most versatile and compact memory solution for high performance, low power, board constraint memory applications.

The 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O offers a multi-partition, dual-operation flash architecture that enables the device to read from one partition while programming or erasing in another partition. This Read-While-Write or Read-While-Erase capability makes it possible to achieve higher data throughput rates as compared to single partition devices and it allows two processors to interleave code execution because program and erase operations can now occur as background processes.

The 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O incorporates a new Enhanced Factory Programming (EFP) mode to improve 12 V factory programming performance. This new feature helps eliminate manufacturing bottlenecks associated with programming high density flash devices. Compare the EFP program time of 3.5 µs per word to the standard factory program time of 8.0 µs per word and save significant factory programming time for improved factory efficiency.

Additionally, the 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O includes block lock-down, programmable WAIT signal polarity and is supported by an array of software tools. All these features make this product a perfect solution for any demanding memory application.

Notice: This document contains preliminary information on new products in production. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

Information in this document is provided in connection with Intel<sup>®</sup> products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 1.8 Volt Intel<sup>®</sup> Wireless Flash Memory (with 3 Volt I/O and SRAM) may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright @ Intel Corporation, 2000 - 2001.

\*Other names and brands may be claimed as the property of others.

| 1.0 | Prod                 | duct Introduction                                       | 1  |  |  |  |  |  |  |  |  |  |

|-----|----------------------|---------------------------------------------------------|----|--|--|--|--|--|--|--|--|--|

|     | 1.1 Document Purpose |                                                         |    |  |  |  |  |  |  |  |  |  |

|     | 1.2                  | Nomenclature                                            | 1  |  |  |  |  |  |  |  |  |  |

| 2.0 | Product Description  |                                                         |    |  |  |  |  |  |  |  |  |  |

|     | 2.1                  | Product Overview                                        |    |  |  |  |  |  |  |  |  |  |

|     | 2.2                  | Package Diagram                                         |    |  |  |  |  |  |  |  |  |  |

|     | 2.3                  | Package Dimensions                                      |    |  |  |  |  |  |  |  |  |  |

|     | 2.4                  | Signal Descriptions                                     |    |  |  |  |  |  |  |  |  |  |

|     | 2.5<br>2.6           | Block Diagram Flash Memory Map                          |    |  |  |  |  |  |  |  |  |  |

| 3.0 |                      | duct Operations                                         |    |  |  |  |  |  |  |  |  |  |

|     | 3.1                  | Bus Operations                                          |    |  |  |  |  |  |  |  |  |  |

|     | 3.2                  | Flash Command Definitions                               |    |  |  |  |  |  |  |  |  |  |

| 4.0 | Flac                 | h Read Modes                                            |    |  |  |  |  |  |  |  |  |  |

| 4.0 |                      |                                                         |    |  |  |  |  |  |  |  |  |  |

|     | 4.1                  | Read Array4.1.1 Asynchronous Mode                       |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.1.2 Synchronous Mode                                  |    |  |  |  |  |  |  |  |  |  |

|     | 4.2                  | Set Configuration Register (CR)                         |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.2.1 Read Mode (RM)                                    |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.2.2 First Latency Count (LC2–0)                       |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.2.3 WAIT Signal Polarity (WT)                         | 16 |  |  |  |  |  |  |  |  |  |

|     |                      | 4.2.4 WAIT Signal Function                              |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.2.5 Data Output Configuration (DOC)                   |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.2.6 WAIT Configuration (WC)                           |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.2.7 Burst Sequence (BS)                               |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.2.8 Clock Configuration (CC)                          |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.2.9 Burst Wrap (BW)                                   |    |  |  |  |  |  |  |  |  |  |

|     | 4.3                  | Read Query Register                                     |    |  |  |  |  |  |  |  |  |  |

|     | 4.4                  | Read ID Register                                        |    |  |  |  |  |  |  |  |  |  |

|     | 4.5                  | Read Status Register                                    |    |  |  |  |  |  |  |  |  |  |

|     |                      | 4.5.1 Clear Status Register                             |    |  |  |  |  |  |  |  |  |  |

|     | 4.6                  | Read-While-Write/Erase                                  | 24 |  |  |  |  |  |  |  |  |  |

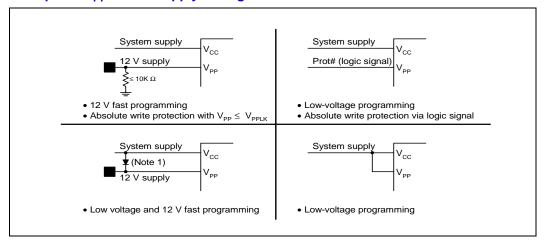

| 5.0 | Prog                 | gram and Erase Voltages                                 | 24 |  |  |  |  |  |  |  |  |  |

|     | 5.1                  | Factory Program Mode                                    |    |  |  |  |  |  |  |  |  |  |

|     | 5.2                  | Programming Voltage Protection (VPP)                    |    |  |  |  |  |  |  |  |  |  |

|     | 5.3                  | Enhanced Factory Programming (EFP)                      |    |  |  |  |  |  |  |  |  |  |

|     |                      | 5.3.1 EFP Requirements and Considerations               |    |  |  |  |  |  |  |  |  |  |

|     |                      | 5.3.2 Setup Phase                                       |    |  |  |  |  |  |  |  |  |  |

|     |                      | 5.3.3 Program Phase                                     |    |  |  |  |  |  |  |  |  |  |

|     |                      | 5.3.4 Verify Phase                                      |    |  |  |  |  |  |  |  |  |  |

|     | 5.4                  | Write Protection (V <sub>PP</sub> < V <sub>PPLK</sub> ) |    |  |  |  |  |  |  |  |  |  |

|     | J. <del>T</del>      | **************************************                  |    |  |  |  |  |  |  |  |  |  |

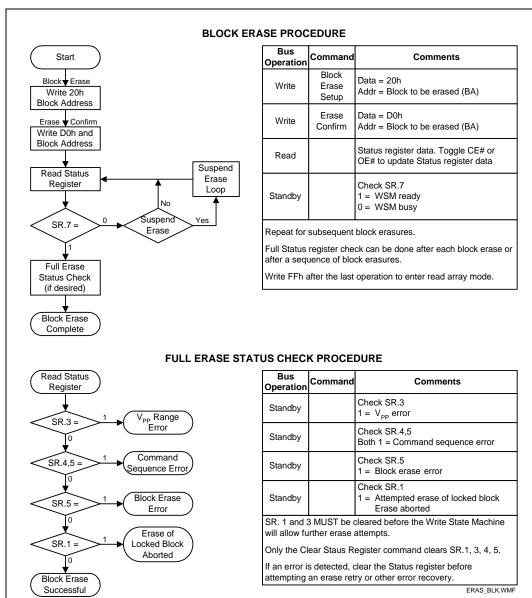

| 6.0           | Flasi        | h Erase Mode                                                | 27 |

|---------------|--------------|-------------------------------------------------------------|----|

|               | 6.1          | Block Erase                                                 | 27 |

|               | 6.2          | Erase Protection (V <sub>PP</sub> < V <sub>PPLK</sub> )     | 28 |

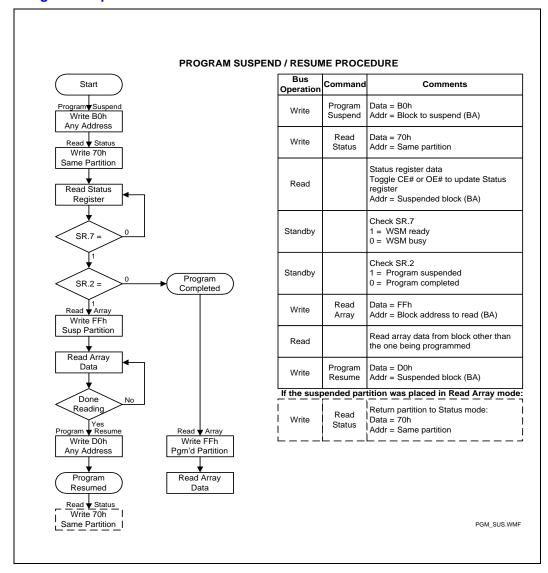

| 7.0           | Flasi        | h Suspend/Resume Modes                                      | 28 |

|               | 7.1          | Program/Erase Suspend                                       |    |

|               | 7.2          | Program/Erase Resume                                        | 28 |

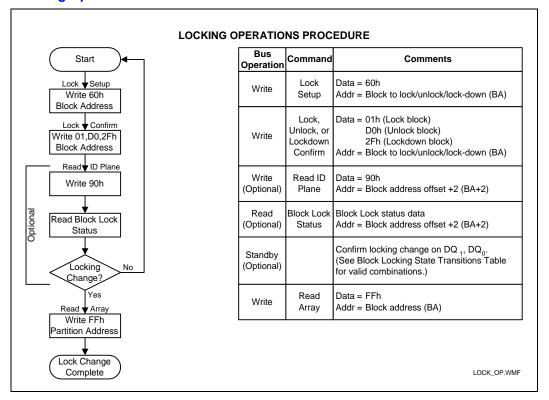

| 8.0           | Flasi        | h Security Modes                                            | 29 |

|               | 8.1          | Block Lock                                                  |    |

|               | 8.2          | Block Unlock                                                |    |

|               | 8.3<br>8.4   | Lock-Down Block  Block Lock Operations during Erase Suspend |    |

|               | 8.5          | WP# Lock-Down Control                                       |    |

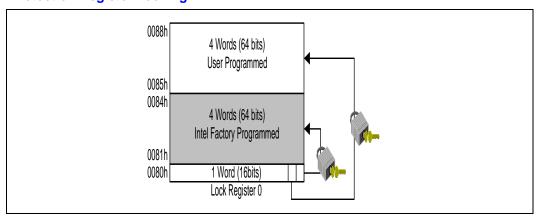

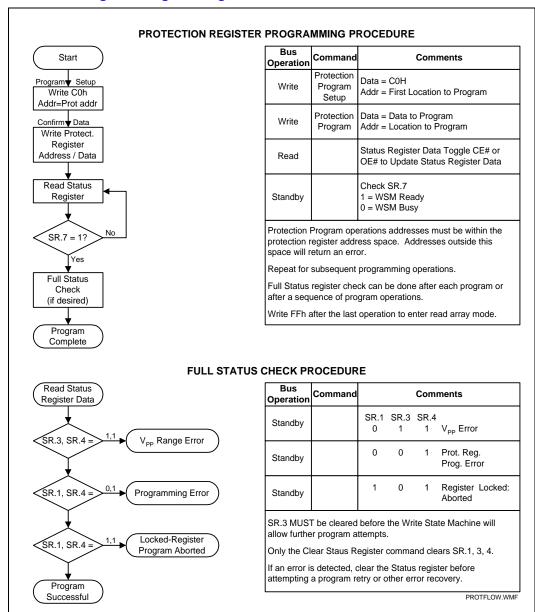

| 9.0           | Flasi        | h Protection Register                                       | 32 |

|               | 9.1          | Protection Register Read                                    |    |

|               | 9.2          | Program Protection Register                                 |    |

|               | 9.3          | Protection Register Lock                                    | 33 |

| 10.0          | Powe         | er and Reset Considerations                                 | 34 |

|               | 10.1         | Power-Up/Down Characteristics                               |    |

|               | 10.2         | Power Supply Decoupling                                     |    |

|               | 10.3         | Flash Reset Characteristics                                 |    |

| 11.0          |              | trical Specifications                                       |    |

|               | 11.1         | Absolute Maximum Ratings                                    |    |

|               | 11.2<br>11.3 | Extended Temperature Operation                              |    |

|               | 11.4         | Discrete Capacitance (32-Mbit VF BGA Package)               |    |

|               | 11.5         | Stacked Capacitance (32/4 and 64/8 Stacked-CSP Package)     |    |

| 12.0          | Flasi        | h AC Characteristics                                        | 40 |

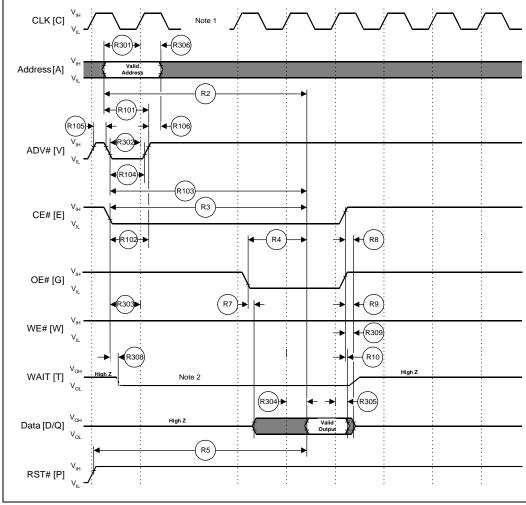

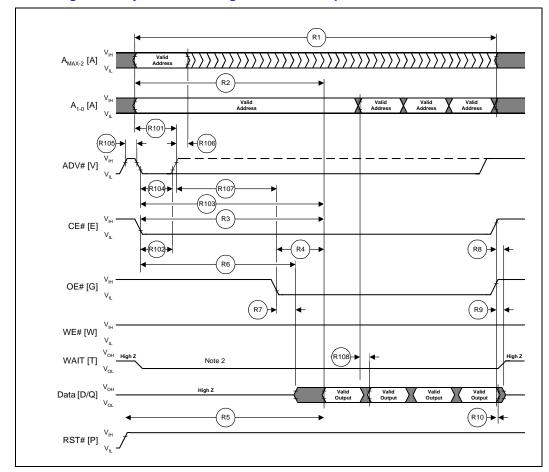

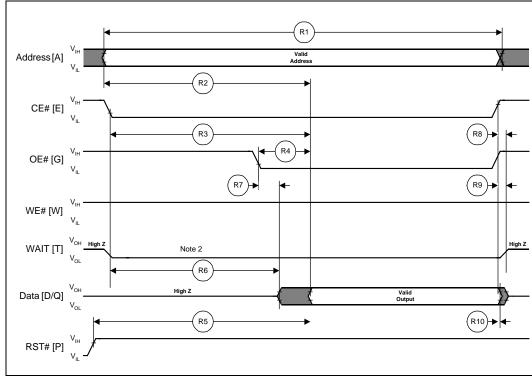

|               | 12.1         | Flash Read Operations                                       | 40 |

|               | 12.2         | Flash Write Operations                                      |    |

|               | 12.3<br>12.4 | Flash Program and Erase Operations                          |    |

| 40.0          |              | •                                                           |    |

| 13.0          |              | M AC Characteristics                                        |    |

|               | 13.1<br>13.2 | SRAM Read Operation SRAM Write Operation                    |    |

|               | 13.2         | SRAM Data Retention Operation                               |    |

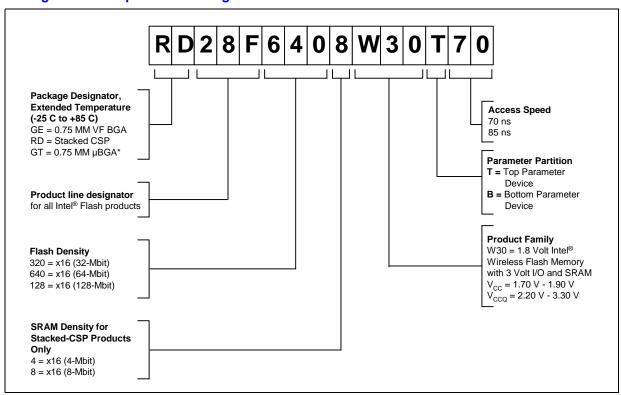

| 14.0          |              | ering Information                                           |    |

| Append        |              | ash Write State Machine (WSM)                               |    |

| • •           |              | · · · · ·                                                   |    |

| Append        |              | owcharts                                                    |    |

| <b>Append</b> | ix C Co      | ommon Flash Interface                                       | 68 |

# **Revision History**

| Date of Revision | Version      | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 09/19/00         | -001         | Original Version                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 09/19/00         | -001<br>-002 | Original Version  28F3208W30 product references removed (product was discontinued)  28F640W30 product added Revised Table 2, Signal Descriptions (DQ <sub>15-0</sub> , ADV#, WAIT, S-UB#, S-LB#, V <sub>CCQ</sub> ) Revised Section 3.1, Bus Operations Revised Table 5, Command Bus Definitions, Notes 1 and 2 Revised Section 4.2.2, First Latency Count (LC <sub>2-0</sub> ); revised Figure 6, Data Output with LC Setting at Code 3; added Figure 7, First Access Latency Configuration Revised Section 4.2.3, WAIT Signal Polarity (WT) Added Section 4.2.4, WAIT Signal Function Revised Section 4.2.5, Data Output Configuration (DOC) Added Figure 8, Data Output Configuration with WAIT Signal Delay Revised Table 13, Status Register DWS and PWS Description Revised entire Section 5.0, Program and Erase Voltages Revised entire Section 5.3, Enhanced Factory Programming (EFP) Revised entire Section 8.0, Flash Security Modes Revised entire Section 9.0, Flash Protection Register, added Table 15, Simultaneous Operations Allowed with the Protection Register Revised Section 10.1, Power-Up/Down Characteristics Revised Section 10.1, Power-Up/Down Characteristics Revised Section 11.3, DC Characteristics. Changed I <sub>CCS</sub> I <sub>CCWS</sub> , I <sub>CCES</sub> Specs from 18 µA to 21µA; changed I <sub>CCR</sub> Spec from 12 mA to 15 mA (burst length = 4) Added Figure 20, WAIT Signal in Synchronous Non-Read Array Operation Waveform Added Figure 21, WAIT Signal in Asynchronous Page-Mode Read Operation Waveform Revised Figure 23, Write Waveform Revised Section 12.4, Reset Operations Clarified Section 13.2, SRAM Write Operation, Note 2 Revised Section 14.0, Ordering Information |

|                  |              | Minor text edits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

# 1.0 Product Introduction

# 1.1 Document Purpose

This document contains information pertaining to the 1.8 Volt Intel® Wireless Flash Memory with 3 Volt I/O and SRAM. Section 1.0 provides a product introduction. Section 2.0 provides a product description. Section 3.0 describes general device operations. Sections 4.0 through 9.0 describe the flash functionality. Section 10 describes device power and reset considerations. Section 11.0 describes the device electrical specifications. Section 12.0 describes the flash AC characteristics. Section 13.0 describes the SRAM AC characteristics. Section 14.0 describes ordering information.

# 1.2 Nomenclature

- Block: a group of flash bits that share common erase circuitry and erase simultaneously.

- **Partition: Partition** is a group of blocks that share erase and program circuitry and a common status register. If one block is erasing or one word is programming, only the status register, rather than array data, is available when any address within the partition is read.

- Main Block: a flash block of 32-Kwords.

- Parameter Block: a flash block of 4-Kwords.

- Main Partition: a partition that only contains main blocks.

- Parameter Partition: a partition that contains both main and parameter blocks.

- **Top/Bottom Parameter Device:** parameter blocks are located at the top/bottom of the flash memory map. A top/bottom parameter partition contains 15 blocks; 7 main blocks and 8 parameter blocks.

# 2.0 Product Description

#### 2.1 Product Overview

Intel<sup>®</sup> 1.8 Volt Wireless Flash Memory with 3 Volt I/O and SRAM combines flash and SRAM into one package. The 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O divides the flash memory into many separate 4-Mbit partitions. By doing this, the device can perform simultaneous read-while-write or read-while-erase operations. With this new architecture, the 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O can read from one partition while programming or erasing in another partition. This read-while-write or read-while-erase capability greatly increases data throughput performance.

Each partition contains eight 32-Kword blocks, called "main blocks." However, for a top or bottom parameter device, the upper or lower 32-Kword block is segmented into eight, separate 4-Kword blocks, called "parameter blocks." Parameter blocks are ideally suited for frequently updated variables or boot code storage. Both main and parameter blocks support page and burst mode reads.

The 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O also incorporates a new Enhanced Factory Programming (EFP) mode. In EFP mode, this device provides the fastest NOR flash factory programming time possible at 3.5 µs per data word. This feature can greatly reduce factory flash programming time and thereby increase manufacturing efficiency.

The 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O offers both hardware and software forms of data protection. Software can individually lock and unlock any block for "on-the-fly" run-time data protection. For absolute data protection, all blocks are locked when the  $V_{PP}$  voltage falls below the  $V_{PP}$  lockout threshold.

Upon initial power up or return from reset, the 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O defaults to page mode. To enable burst mode, write and configure the configuration register. While in burst mode, the 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O is synchronized with the host CPU. Additionally, a configurable WAIT signal can be used to provide easy flash-to-CPU synchronization.

The 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O maintains compatibility with Intel<sup>®</sup> Command User Interface (CUI), Common Flash Interface (CFI), and Intel<sup>®</sup> Flash Data Integrator (FDI) software tools. CUI is used to control the flash device, CFI is used to obtain specific product information, and FDI is used for data management.

The 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM offers two low-power savings features: Automatic Power Savings (APS) and standby mode. The flash device automatically enters APS following the completion of any read cycle. Flash and SRAM standby modes are enabled when the appropriate chip select signals are de-asserted.

Finally, the 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O provides program and erase suspend/resume operations to allow system software to service higher priority tasks. It offers a 128-bit protection register that can be used for unique device identification and/or system security purposes.

Combined, all these features make the 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O and SRAM an ideal solution for any high-performance, low-power, board-constrained memory application.

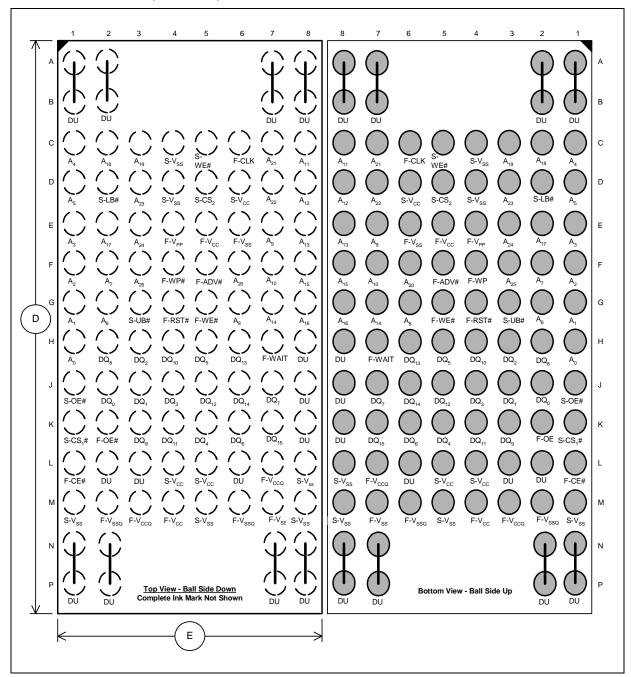

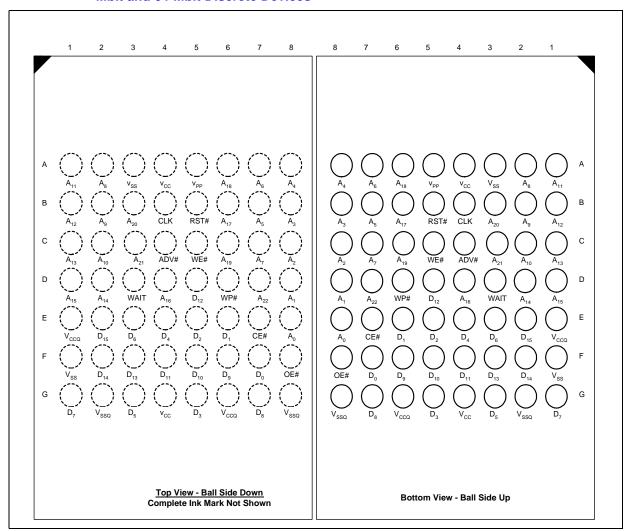

# 2.2 Package Diagram

Figure 1. 80-Ball Matrix, 0.80 mm Ball Pitch, Stacked-CSP for 32/4-, 64/8- and 128/TBD-Mbit Devices (Flash + SRAM)

#### NOTES:

On lower density devices, upper address balls can be treated as no connects. For example, on a 32-Mbit device, A<sub>23-21</sub> will be no connects.

Figure 2. 56-Ball Matrix, 0.75 mm Ball Pitch, VF BGA Package and μBGA\* Package for the 32-Mbit and 64-Mbit Discrete Devices

#### NOTE

1. All balls will be populated; however, addresses  $A_{21}$  and  $A_{22}$  will be NC.

# 2.3 Package Dimensions

**Table 1. Package Outline Dimensions**

| Package<br>Type | Device<br>Density      | Dimension-D<br>(± 0.1 mm) | Dimension-E<br>(± 0.1 mm) | Height<br>(max.) (mm) |

|-----------------|------------------------|---------------------------|---------------------------|-----------------------|

| VF BGA          | 32 Mbit                | 7.7 mm                    | 9.0 mm                    | 1.0 mm                |

| μBGA*           | μBGA* 64 Mbit          |                           | 9.0 mm                    | 1.0 mm                |

| Stacked-CSP     | Stacked-CSP 32/4, 64/8 |                           | 8.0 mm                    | 1.4 mm                |

# 2.4 Signal Descriptions

Table 2. Signal Descriptions (Sheet 1 of 2)

| Symbol              | Type | Name and Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ۸                   | ı    | ADDRESS: Device address. Addresses are internally latched during read and write cycles.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| A <sub>25-0</sub>   | '    | 32-Mbit flash: A <sub>20-0</sub> ; 64-Mbit flash: A <sub>21-0</sub> ; 128-Mbit flash: A <sub>22-0</sub> ; 4-Mbit SRAM: A <sub>17-0</sub> ; 8-Mbit SRAM: A <sub>18-0</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| DQ <sub>15-0</sub>  | I/O  | <b>DATA INPUT/OUTPUTS:</b> Inputs data and commands during write cycles, outputs data during query, id reads, memory, status register, protection register, and configuration code reads. Data signals float when the chip or outputs are deselected. Data is internally latched during writes. Query accesses and status register accesses use DQ <sub>0</sub> -DQ <sub>7</sub> . All other accesses use DQ <sub>0</sub> -DQ <sub>15</sub> .                                                                                                                                                                                                                                                                       |

| ADV#                | I    | <b>FLASH ADDRESS VALID:</b> Internally latches addresses. In page mode, addresses are internally latched on the rising edge of ADV#. In burst mode, address internally latched on the rising edge of ADV# or rising/falling edge of CLK, whichever occurs first. Connect ADV# to GND when the flash device is operating in asynchronous mode only.                                                                                                                                                                                                                                                                                                                                                                  |

| CE#                 | I    | <b>FLASH CHIP ENABLE:</b> Enables/disables flash device. CE#-low enables the device. CE#-high disables the device and places the device into standby mode. CE# high places data and WAIT signals at a High-Z level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

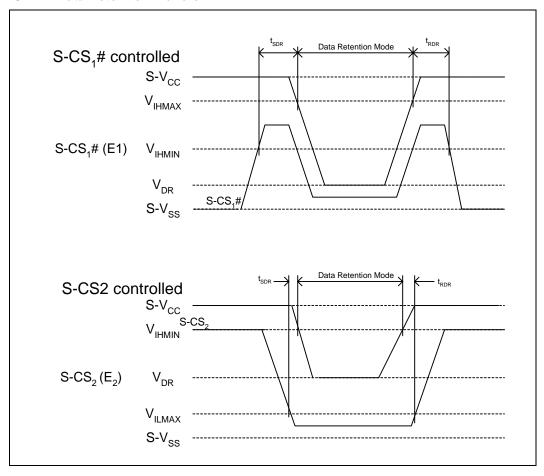

| S-CS <sub>1</sub> # | ı    | <b>SRAM CHIP SELECT1:</b> Activates the SRAM internal control logic, input buffers, decoders and sense amplifiers. S-CS <sub>1</sub> # is active low. S-CS <sub>1</sub> # high deselects the SRAM memory device and reduces power consumption to standby levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| S-CS <sub>2</sub>   | I    | <b>SRAM CHIP SELECT2:</b> Activates the SRAM internal control logic, input buffers, decoders and sense amplifiers. S-CS <sub>2</sub> is active high. S-CS <sub>2</sub> low deselects the SRAM memory device and reduces power consumption to standby levels.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

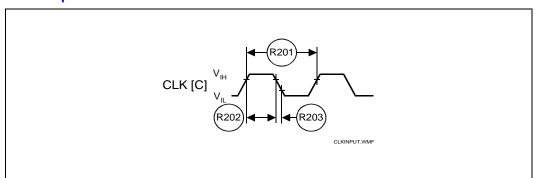

| CLK                 | I    | FLASH CLOCK: Synchronizes the device to the system bus frequency. (Used only in burst mode.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| OE#                 | I    | <b>FLASH OUTPUT ENABLE:</b> Enables/disables device output buffers. OE# low enables the device output buffers. OE# high disables the device output buffers and places all outputs at a High-Z level.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| S-OE#               | I    | SRAM OUTPUT ENABLE: Activates the SRAM outputs through the data buffers during a read operation. S-OE# is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RST#                | I    | <b>FLASH RESET:</b> Enables/disables device operation. RST# low initializes internal circuitry and disables device operation. RST# high enables device operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| WAIT                | 0    | <b>FLASH WAIT:</b> Indicates valid data in burst read mode. WAIT is at High-Z until the configuration register bit CR.10 is set, which also determines its polarity when asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| WE#                 | I    | <b>FLASH WRITE ENABLE:</b> Enables/disables device write buffers. WE# low enables the device write buffers. Data is latched on the rising edge of WE#. WE# high disables the device write buffers.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| S-WE#               | I    | SRAM WRITE ENABLE: Controls writes to the SRAM memory array. S-WE# is active low.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| S-UB#               | I    | <b>SRAM UPPER BYTE ENABLE:</b> Enables the upper bytes for SRAM (DQ <sub>15-8</sub> ). S-UB# is active low. S-UB# and S-LB# must be tied together to restrict x16 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| S-LB#               | I    | <b>SRAM LOWER BYTE ENABLE:</b> Enables the lower bytes for SRAM (DQ <sub>7-0</sub> ). S-LB# is active low. S-UB# and S-LB# must be tied together to restrict x16 mode.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| WP#                 | I    | <b>FLASH WRITE PROTECT:</b> Enables/disables the device lock-down function. WP# low enables the lock-down mechanism and blocks marked lock-down cannot be unlocked by system software. WP# high disables the lock-down mechanism and blocks marked lock-down can be unlocked by system software.                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V <sub>PP</sub>     | Pwr  | <b>FLASH PROGRAM/ERASE POWER:</b> Hardware erase and program protection. A valid $V_{PP}$ voltage on this ball allows erase or programming. Memory contents cannot be altered when $V_{PP} \leq V_{PPLK}$ . Block erase and program at invalid $V_{PP}$ voltages should not be attempted. Set $V_{PP} = V_{CC}$ for in-system read, program, and erase operations. $V_{PP}$ must remain above $V_{PP1}$ Min to perform in-system operations. $V_{PP2}$ can be applied to main blocks for 1000 cycles maximum and to parameter blocks for 2500 cycles. $V_{PP}$ can be $V_{PP2}$ for a cumulative total, not to exceed 80 hours maximum. Extended use of this ball at $V_{PP2}$ may reduce block cycling capability. |

| V <sub>CC</sub>     | Pwr  | FLASH POWER SUPPLY: Flash operations at invalid V <sub>CC</sub> voltages should not be attempted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| $V_{CCQ}$           | Pwr  | FLASH OUTPUT POWER SUPPLY: Enables all input and output signals to be driven at V <sub>CCQ</sub> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

Table 2. Signal Descriptions (Sheet 2 of 2)

| Symbol            | Туре | Name and Function                                                                                                                                           |

|-------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>SS</sub>   | Pwr  | <b>FLASH POWER SUPPLY GROUND:</b> Balls for internal device circuitry must be connected to system ground.                                                   |

| V <sub>SSQ</sub>  | Pwr  | FLASH OUTPUT POWER SUPPLY GROUND: Balls for internal device circuitry must be connected to system ground.                                                   |

| S-V <sub>CC</sub> | Pwr  | SRAM POWER SUPPLY: Device operations at invalid S-V <sub>CC</sub> voltages should not be attempted.                                                         |

| S-V <sub>SS</sub> | Pwr  | SRAM GROUND: Balls for all internal device circuitry must be connected to system ground.                                                                    |

| DU                |      | <b>DON'T USE:</b> Do not use this ball. This ball should not be connected to any power supplies, control signals and/or any other ball and must be floated. |

| NC                |      | NO CONNECT: No internal connection. Can be driven or floated.                                                                                               |

**NOTE:** For non-discrete devices, all flash signals are prefixed with F\_ before its signal's name.

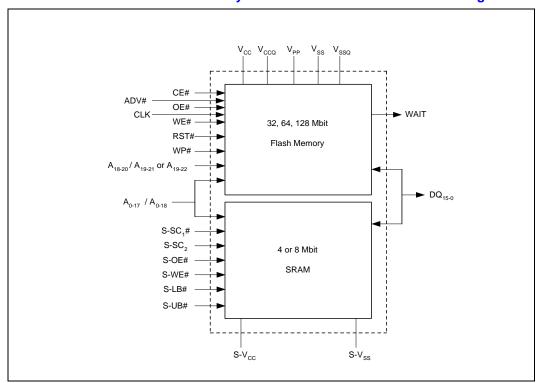

# 2.5 Block Diagram

Figure 3. 1.8 Volt Intel® Wireless Flash Memory with 3 Volt I/O and SLRAM Block Diagram

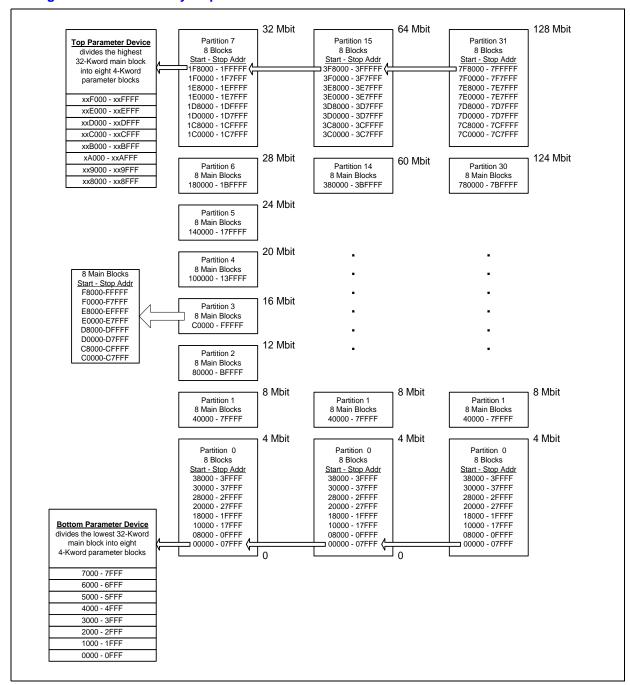

# 2.6 Flash Memory Map

The 1.8 Volt Intel<sup>®</sup> Wireless Flash Memory with 3 Volt I/O memory is divided into separate partitions to support the read-while-write/erase function. Each partition is 4-Mbits in size and can operate independently from other partitions.

#### 28F6408W30, 28F3204W30, 28F320W30, 28F640W30

A 32-Mbit device will have eight partitions; a 64-Mbit device will have 16 partitions; a 128-Mbit device will have 32 partitions. Each main block is 32-Kword in size.

The 1.8 Volt Intel Wireless Flash Memory with 3 Volt I/O supports CPUs that boot from either the top or bottom of the flash memory map. A top parameter flash device has the highest addressable 32-Kword block divided into eight smaller blocks. Conversely, a bottom parameter flash device has the lowest addressable 32-Kword block divided into eight smaller blocks. Each of these eight 4-Kword blocks are called parameter blocks. Parameter blocks are useful for frequently stored data variables. Their smaller block size allows them to erase faster than main blocks. Page- and burst-mode reads are also permitted in all blocks and across all partition boundaries.

It should be mentioned that the SRAM does not adhere to this multi-partition architecture. The SRAM memory is organized as a single memory array.

Figure 4. Flash Memory Map

#### NOTES:

- 1. Partition size: 4 Mbit/256 Kword/512 Kbytes.

- 2. Main block size: 32 Kword/64 Kbytes.

- 3. Parameter block size: 4 Kword/8 Kbytes.

- 4. All partitions have 8 main blocks, except for top/bottom parameter partitions.

- 5. Top/bottom parameter partitions have 15 blocks, 7 main and 8 parameter.

# 3.0 Product Operations

# 3.1 Bus Operations

The 1.8 Volt Intel® Wireless Flash Memory's on-chip Write State Machine (WSM) manages erase and program algorithms. The local CPU controls the in-system read, program, and erase operations of the flash device. Bus cycles to and from the flash device conform to standard microprocessor bus operations. RST#, CE#, OE#, WE#, and ADV# signals control the flash. WAIT informs the CPU of valid data during burst reads. S-OE#, S-WE#, S-CS<sub>1</sub>#, S-CS<sub>2</sub>, S-LB# and S-UB# control the SRAM. S-UB# and S-LB# must be tied together to restrict x16 mode. Table 3 summarizes bus operations.

**Table 3. Bus Operations**

|       | Mode           | Note   | RST#            | CE#                            | # <b>3</b> 0    | WE#             | ADV#            | WAIT            | S-CS <sub>1</sub> # | S-CS <sub>2</sub> | 8-0E#           | S-WE#    | S-UB#<br>S-LB# <sup>7</sup> | DQ<br>[15:0]     |

|-------|----------------|--------|-----------------|--------------------------------|-----------------|-----------------|-----------------|-----------------|---------------------|-------------------|-----------------|----------|-----------------------------|------------------|

|       | Read           | 1,2, 5 | V <sub>IH</sub> | V <sub>IL</sub>                | V <sub>IL</sub> | V <sub>IH</sub> | V <sub>IL</sub> | Valid           | S                   | RAM r             | nust be         | in Hig   | h-Z                         | D <sub>OUT</sub> |

|       | Output Disable | 3      | $V_{IH}$        | $V_{IL}$                       | $V_{IH}$        | V <sub>IH</sub> | Х               | High-Z          |                     |                   |                 |          |                             | High-Z           |

| FLASH | Standby        | 3      | V <sub>IH</sub> | V <sub>IH</sub>                | Х               | Х               | Х               | High-Z          |                     | Any Va            | ılid SR         | АМ Мо    | de                          | High-Z           |

|       | Reset 3        |        | V <sub>IL</sub> | Х                              | Х               | Х               | Х               | High-Z          |                     |                   |                 |          | High-Z                      |                  |

|       | Write          | 4, 5   | $V_{IH}$        | $V_{IL}$                       | $V_{IH}$        | $V_{IL}$        | $V_{IL}$        | High-Z          | S                   | SRAM r            | nust be         | in Hig   | h Z                         | D <sub>IN</sub>  |

|       | Read           | 5      | FI              | ash mu                         | ust be i        | n High          | -Z              | High-Z          | $V_{IL}$            | $V_{IH}$          | $V_{IL}$        | $V_{IH}$ | $V_{IL}$                    | D <sub>OUT</sub> |

|       | Output Disable | 3      |                 | •                              |                 |                 |                 |                 | $V_{IL}$            | $V_{IH}$          | V <sub>IH</sub> | $V_{IH}$ | Χ                           | High-Z           |

| SRAM  | Standby and    | 3, 6   |                 | Any Valid FLASH Mode           |                 |                 | )               | V <sub>IH</sub> | Х                   | Х                 | Х               | Χ        | High-Z                      |                  |

|       | Data Retention | 3, 0   |                 |                                |                 |                 |                 |                 | Х                   | $V_{IL}$          | Х               | Х        | Х                           | High-Z           |

|       | Write          | 5      | FI              | Flash must be in High-Z High-Z |                 |                 |                 | High-Z          | $V_{IL}$            | $V_{IH}$          | V <sub>IH</sub> | $V_{IL}$ | $V_{IL}$                    | D <sub>IN</sub>  |

#### NOTES:

- 1. Manufacturer and device ID codes are accessed by Read ID Register command.

- 2. Query and status register accesses use only DQ<sub>7-0</sub>. All other accesses use DQ<sub>15-0</sub>.

- 3. X must be  $V_{\text{IL}}$  or  $V_{\text{IH}}$  for control signals and addresses.

- 4. Refer to Table 5, "Command Bus Definitions" on page 11 for valid D<sub>IN</sub> during a write operation.

- 5. Two devices may not drive the memory bus at the same time.

- The SRAM can be placed into data retention mode by lowering the S-V<sub>CC</sub> to the V<sub>DR</sub> limit when in standby mode.

- 7. Always tie S-UB# and S-LB# together.

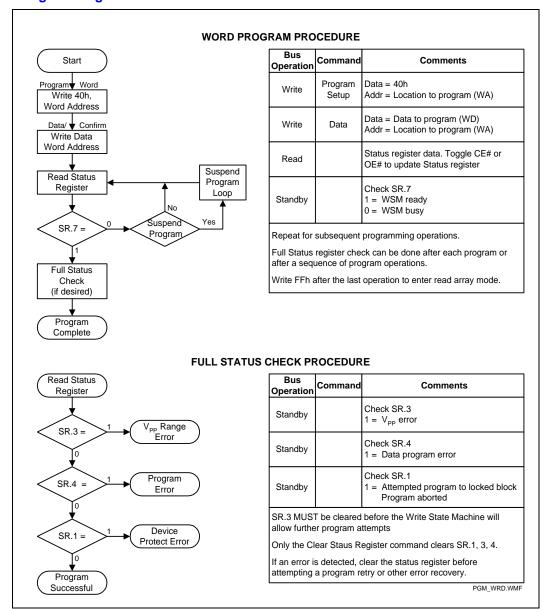

#### 3.2 Flash Command Definitions

Device operations are selected by writing specific commands to the Command User Interface (CUI). Table 4, "Command Code and Descriptions" on page 10 lists all possible command codes and descriptions. Table 5, "Command Bus Definitions" on page 11 further defines command bus cycle operations. Since commands are partition-specific, it is important to write commands within the target partition range.

Multi-cycle command writes to the flash memory partition must be issued sequentially without intervening command writes. For example, an Erase Setup command to partition X must be immediately followed by the Erase Confirm command in order to be executed properly. The address given during the Erase Confirm command determines the location of the erase. If the Erase

Confirm command is given to partition X, then the command will be executed, and a block in partition X will be erased. Alternatively, if the Erase Confirm command is given to partition Y, the command will still be executed, and a block in partition Y will be erased. Any other command given to ANY partition prior to the Erase Confirm command will result in a command sequence error, which is posted in the status register. After the erase has successfully started in partition X or Y, read cycles can occur in any other partition.

Table 4. Command Code and Descriptions (Sheet 1 of 2)

| Mode          | Instruction<br>Code | Command                                             | Description                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

|---------------|---------------------|-----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|               | FFh                 | Read Array                                          | Places addressed partition in read array mode.                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|               | 70h                 | Read Status<br>Register                             | Places addressed partition in read status register mode. A partition automatically enters the read status register mode after a valid Program/Erase command is executed.                                                                                                                                                                                                                                               |  |  |  |  |  |  |

| Read          | 90h                 | Read ID Register,<br>Read Configuration<br>Register | Puts the addressed partition in read device identifier mode. The device outputs manufacturer and device ID codes, configuration register settings, block lock status and protection register data. Data is output on DQ <sub>15-0</sub> .                                                                                                                                                                              |  |  |  |  |  |  |

|               | 98h                 | Read Query<br>Register                              | Puts the addressed partition in read query mode. The device outputs Common Flash Interface (CFI) information on DQ <sub>7-0</sub> .                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

|               | 50h                 | Clear Status<br>Register                            | Clears status register bits 1, 3, 4 and 5. The WSM can set (1) and reset (0) bits 0, 2, 6 and 7.                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|               | 40h                 | Word Program<br>Setup                               | The preferred first bus cycle program command that prepares the WSM for a program operation. The second bus cycle command latches the address and data. A Read Array command is required to read array data after programming.                                                                                                                                                                                         |  |  |  |  |  |  |

| am            | 10h                 | Alternate Word<br>Program Setup                     | Equivalent to a Word Program Setup command (40h).                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| Program       | 30h                 | Enhanced Factory<br>Programming<br>Setup            | Activates Enhanced Factory Programming mode (EFP). The first bus cycle sets up the command. If the second bus cycle is a Confirm command (D0h), subsequent writes provide program data. All other commands are ignored once EFP mode begins.                                                                                                                                                                           |  |  |  |  |  |  |

|               | D0h                 | Enhanced Factory<br>Programming<br>Confirm          | If the first command was Enhanced Factory Programming Setup (30h), the CUI latches the address, confirms command data, and prepares the device for EFP mode.                                                                                                                                                                                                                                                           |  |  |  |  |  |  |

|               |                     |                                                     | Prepares the WSM for a block erase operation. The device erases the block addressed by the Erase Confirm command. If the next command is not Erase Confirm, the CUI                                                                                                                                                                                                                                                    |  |  |  |  |  |  |

| Erase         | 20h                 | Block Erase Setup                                   | (a) sets status register bits SR.4 and SR.5 to "1,"  (b) places the partition in the read status register mode  (c) waits for another command.                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

| ш             | D0h                 | Erase Confirm                                       | If the first command was Erase Setup (20h), the WSM latches address and data and erases the block indicated by the erase confirm cycle address. During program/erase, the partition responds only to Read Status Register, Program Suspend, and Erase Suspend commands. CE# or OE# toggle updates status register data.                                                                                                |  |  |  |  |  |  |

| Suspend       | B0h                 | Program or<br>Erase Suspend                         | This command issued at any device address initiates suspension of the currently executing program/erase operation. The status register, invoked by a Read Status Register command, indicates successful operation suspension by setting (1) status bits SR.2 (program suspend) or SR.6 (erase suspend) and SR.7. The WSM remains in the suspend mode regardless of control signal states, except RST# = $V_{\rm IL}$ . |  |  |  |  |  |  |

| 0             | D0h                 | Suspend Resume                                      | This command issued at any device address resumes suspended program or erase operation.                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |  |

| ng            | 60h                 | Lock Setup                                          | Prepares the WSM lock configuration. If the next command is not Block-Lock, Unlock, or Lock-Down the WSM sets SR.4 and SR.5 to indicate command sequence error.                                                                                                                                                                                                                                                        |  |  |  |  |  |  |

| S.            | 01h                 | Lock Block                                          | If the previous command was Lock Setup (60h), the CUI locks the addressed block.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Block Locking | D0h                 | Unlock Block                                        | After a Lock Setup (60h) command the CUI latches the address and unlocks the addressed block. If previously Locked-down, the operation has no effect.                                                                                                                                                                                                                                                                  |  |  |  |  |  |  |

| ЭЩ            | 2Fh                 | Lock-Down                                           | After a Lock Setup (60h) command, the CUI latches the address and locks-down the addressed block.                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

Table 4. Command Code and Descriptions (Sheet 2 of 2)

| Mode          | Instruction<br>Code | Command           | Description                                                                                                                                                                                                                      |

|---------------|---------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Protection    |                     | Setup             | Prepares the WSM for a protection register program operation. The second bus cycle latches address and data. To read array data after programming, issue a Read Array command.                                                   |

| ation         | hun                 |                   | Prepares the WSM for device configuration. If Set Configuration Register is not the next command, the WSM sets SR.4 and SR.5 to indicate command sequence error.                                                                 |

| Configuration | i u∹n               | Set Configuration | If the previous command was Configuration Setup (60h), the WSM writes data into the configuration register via A <sub>15-0</sub> . Following a Set Configuration Register command, subsequent read operations access array data. |

**NOTE:** Unassigned instruction codes should not be used. Intel reserves the right to redefine these codes for future functions.

**Table 5. Command Bus Definitions**

| e                  | Command                    | Bus        | F     | irst Bus Cyc        | le                    | Se    | cond Bus Cy         | /cle                  |

|--------------------|----------------------------|------------|-------|---------------------|-----------------------|-------|---------------------|-----------------------|

| Mode               | Command                    | Cycles     | Oper  | Addr <sup>(1)</sup> | Data <sup>(2,3)</sup> | Oper  | Addr <sup>(1)</sup> | Data <sup>(2,3)</sup> |

|                    | Read Array                 | 1          | Write | PnA                 | FFh                   |       |                     |                       |

|                    | Read ID Register           | 2          | Write | XnA                 | 90h                   | Read  | XnA+IA              | IC                    |

| READ               | Read Query Register        | 2          | Write | PnA                 | 98h                   | Read  | PnA+QA              | QD                    |

| 8                  | Read Status Register       | 2          | Write | PnA                 | 70h                   | Read  | BA                  | SRD                   |

|                    | Clear Status Register      | 1          | Write | XX                  | 50h                   |       |                     |                       |

|                    | Block Erase                | 2          | Write | ВА                  | 20h                   | Write | BA                  | D0h                   |

| ¥ω                 | Word Program               | 2          | Write | WA                  | 40h/10h               | Write | WA                  | WD                    |

| PROGRAM<br>ERASE   | Enhanced Factory Program   | <u>≥</u> 2 | Write | WA                  | 30h                   | Write | WA                  | D0h                   |

| PRO                | Program/Erase Suspend      | 1          | Write | XX                  | B0h                   |       |                     |                       |

|                    | Program/Erase Resume       | 1          | Write | XX                  | D0h                   |       |                     |                       |

|                    | Lock Block                 | 2          | Write | BA                  | 60h                   | Write | BA                  | 01h                   |

| LOCK               | Unlock Block               | 2          | Write | ВА                  | 60h                   | Write | BA                  | D0h                   |

|                    | Lock-Down Block            | 2          | Write | BA                  | 60h                   | Write | BA                  | 2Fh                   |

| نٰے                | Protection Program         | 2          | Write | PA                  | C0h                   | Write | PA                  | PD                    |

| PROTEC-<br>TION    | Lock Protection Program    | 2          | Write | LPA                 | C0h                   | Write | LPA                 | FFFDh                 |

| CONFIG-<br>URATION | Set Configuration Register | 2          | Write | CD                  | 60h                   | Write | CD                  | 03h                   |

#### NOTES

<sup>1.</sup> First cycle command addresses should be the same as the operation's target address. Examples: the first-cycle address for the Read ID Register command should be the same as the Identification Code address (IA); the first cycle address for the Program command should be the same as the word address (WA) to be programmed; the first cycle address for the Erase/Program Suspend command should be the same as the address within the block to be suspended; etc.

XX = Any valid address within the device.

IA = Identification code address.

BA = Address within the block.

LPA = Lock Protection Address is obtained from the CFI (via the Read Query command). Intel®1.8 Volt

Wireless Flash Memory Flash Memory family's LPA is at 0080h.

PA = User programmable 4-word protection address in the device identification plane.

PnA = Address within the partition.

XnA = Base Address where X can be partition, main block or parameter block. See Figure 11, "Device Identification Codes" on page 21 for details.

QA = Query code address.

WA = Word address of memory location to be written.

2. SRD = Data read from the status register on DQ<sub>7-0</sub>.

WD = Data to be written at location WA.

IC = Identifier code data.

PD =User programmable 4-word protection data.

QD = Query code data on  $DQ_{7-0}$ .

CD = Configuration register code data presented on device addresses  $A_{15-0}$ .  $A_{MAX-16}$  address bits can select any partition. See Table 6, "Configuration Register Bits" on page 13 for configuration register bits descriptions.

3. Commands other than those shown above are reserved by Intel for future device implementations and should not be used.

# 4.0 Flash Read Modes

# 4.1 Read Array

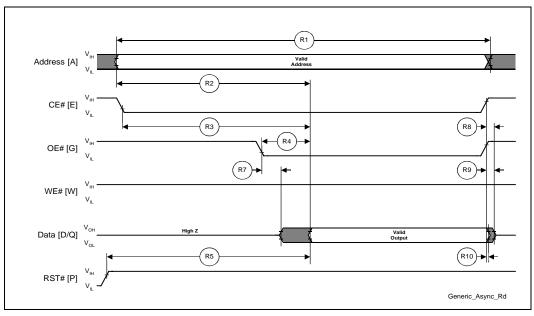

#### 4.1.1 Asynchronous Mode

The 1.8 Volt Intel® Wireless Flash Memory with 3 Volt I/O supports asynchronous reads. An asynchronous read is executed by implementing a read operation without the use of the CLK signal. During an asynchronous read operation, the CLK signal is ignored. If asynchronous reads will be the only read mode of operation, it is recommended that the CLK signal be held at a valid  $V_{\rm IH}$  level.

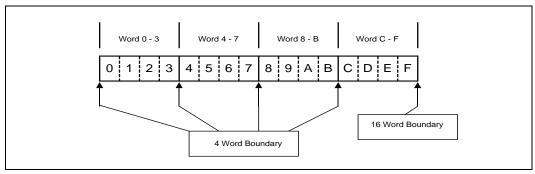

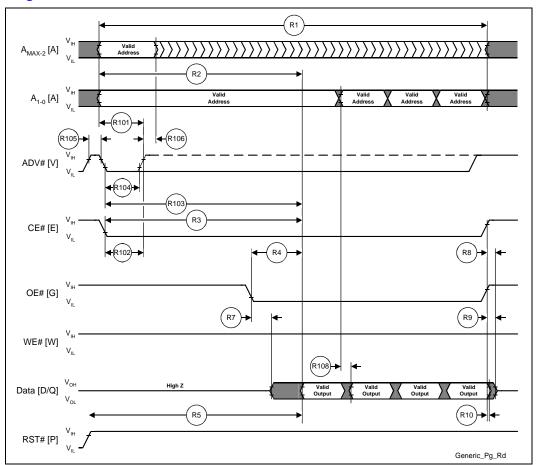

Page mode is the default read mode after power-up or reset. A page-mode read outputs 4 words of asynchronous data; however, by manipulating certain control signals, the device can be made to output less than 4 words.

After power-up or reset, it is not necessary to execute the Read Array command before accessing the flash memory. However, to perform a flash read at any other time, it is necessary to execute the Read Array command before accessing the flash memory.

Page mode is permitted in all blocks, across all partition boundaries and operates independent of  $V_{PP}$  A single-word read can be used to access register information. During asynchronous reads, the address is latched on the rising edge of ADV#.

Upon completion of reading the array, the device automatically enters an Automatic Power Savings (APS) mode. APS mode consumes power comparable to standby mode.

#### 4.1.2 Synchronous Mode

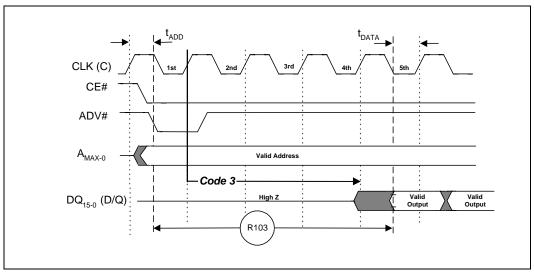

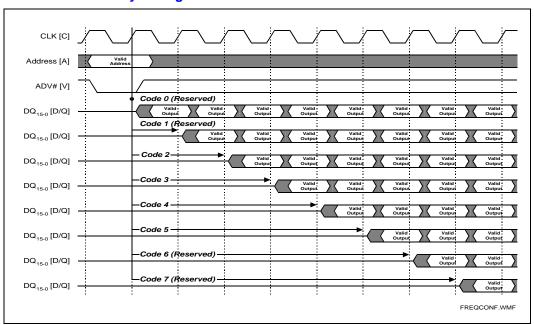

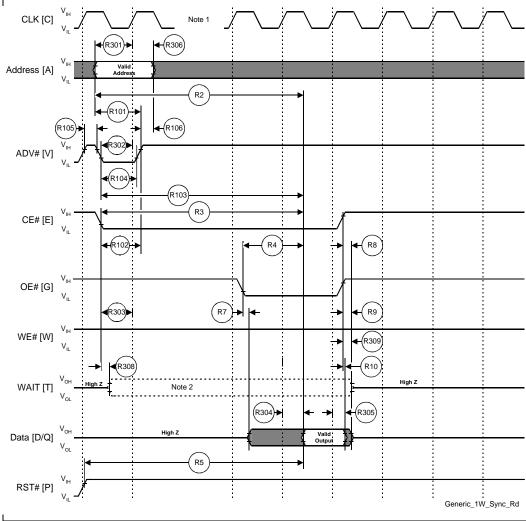

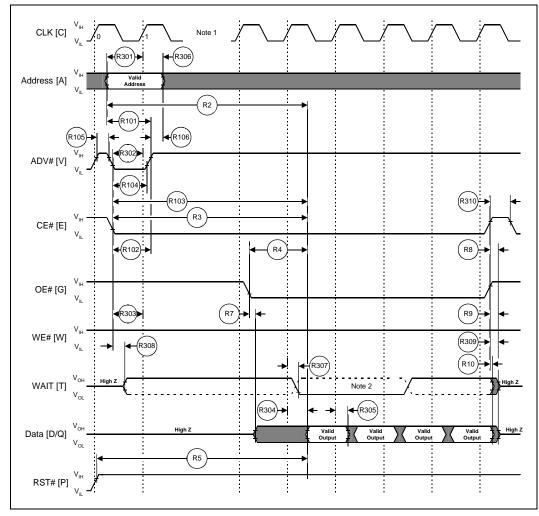

The 1.8 Volt Intel<sup>®</sup> Wireless Flash Memory supports synchronous reads. A synchronous read is executed by implementing a read operation with the use of the CLK signal. During a synchronous read operation, the CLK signal edge (rising or falling) controls flash array access.

A burst-mode read is synchronized to the CLK signal and outputs a 4-, 8- or continuous-word data stream based on configuration register settings. However, by manipulating certain control signals, the device can be made to output less then 4-, 8- or continuous-words.

#### 28F6408W30, 28F3204W30, 28F320W30, 28F640W30

Burst mode is **not** the default mode after power-up or a device reset. To perform a burst-mode read, the configuration register must be set. To set the configuration register, refer to Section 4.2, "Set Configuration Register (CR)" on page 13. After setting the configuration register, if the first device operation is a burst-mode read, it is not necessary to execute the Read Array command before accessing the flash memory. However, to perform a flash read at any other time, it is necessary to execute the Read Array command before accessing the flash memory array.

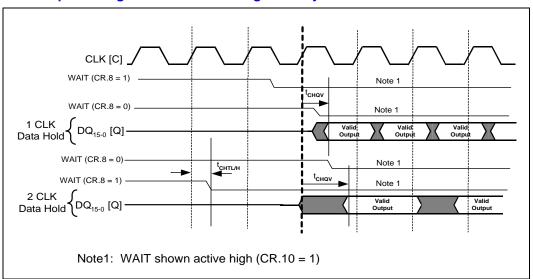

Burst mode is permitted in all blocks, across all partition boundaries and operates independently of  $V_{PP.}$  A single-word burst-mode read **cannot** be used to access register information. In burst mode, the address is latched by either the rising edge of ADV# or the rising edge of CLK with ADV# low, whichever occurs first.

Upon completion of reading the array, the device automatically enters an Automatic Power Savings (APS) mode. APS mode consumes power comparable to standby mode.

# 4.2 Set Configuration Register (CR)

The configuration register is 16 bits wide. This register is used to configure the burst mode parameters. Therefore, if using page mode, it is not necessary to set this register.

To set the configuration register, execute the Set Configuration Register command. The 16 bits of data used by this command must be placed on address lines  $A_{15-0}$ . All other address lines must be held low  $(V_{IL})$ .

After setting the configuration register, if the first device operation is a flash burst-mode read, it is not necessary to execute the Read Array command before accessing the flash memory. However, to perform a burst-mode read at any other time, it is necessary to execute the Read Array command before accessing the flash memory.

#### Table 6. Configuration Register Bits

|                 | Configuration Register Bits <sup>2</sup>                                                                                                                                                                                                              |                   |  |  |    |     |    |    |    |                |                |    |                   |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--|--|----|-----|----|----|----|----------------|----------------|----|-------------------|--|--|

| A <sub>15</sub> | A <sub>15</sub> A <sub>14</sub> A <sub>13</sub> A <sub>12</sub> A <sub>11</sub> A <sub>10</sub> A <sub>9</sub> A <sub>8</sub> A <sub>7</sub> A <sub>6</sub> A <sub>5</sub> A <sub>4</sub> A <sub>3</sub> A <sub>2</sub> A <sub>1</sub> A <sub>0</sub> |                   |  |  |    |     |    |    |    |                |                |    |                   |  |  |

| RM              | R <sup>1</sup>                                                                                                                                                                                                                                        | LC <sub>2-0</sub> |  |  | WT | DOC | WC | BS | СС | R <sup>1</sup> | R <sup>1</sup> | BW | BL <sub>2-0</sub> |  |  |

|                 | 0                                                                                                                                                                                                                                                     |                   |  |  |    |     |    |    |    | 0              | 0              |    |                   |  |  |

#### NOTES:

- 1. 'R' bits are reserved bits. These bits and all other address lines must be set low.

- On power-up or return from reset, all bits are set to "1."

**Table 7. Configuration Register Bit Settings**

| Bit Name                                                  | Setting                                                                                                                                                 |

|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

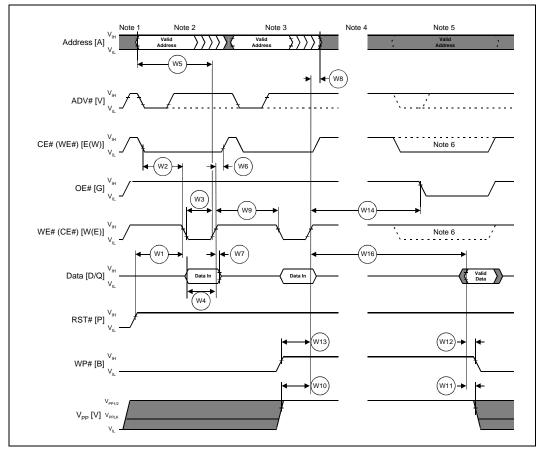

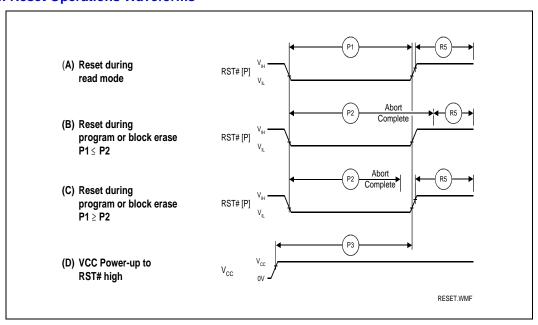

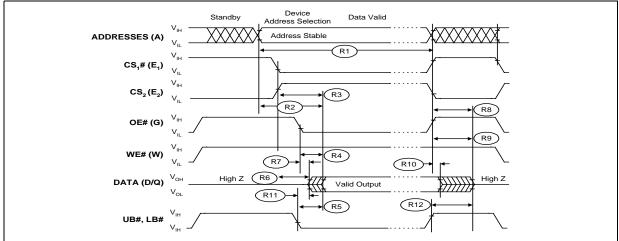

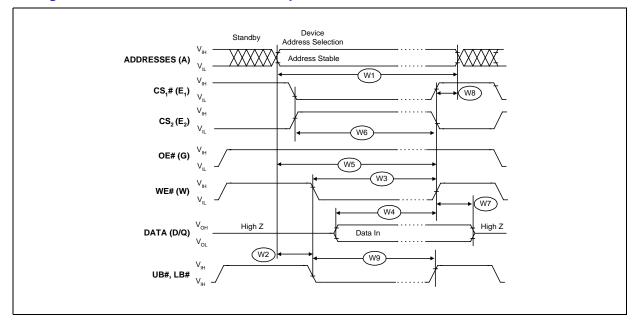

| Read Mode (RM)                                            | 0 = Burst or synchronous mode.                                                                                                                          |